# **DESIGN AMBA BASED** AHB TO APB BRIDGE USING VERILOG HDL

# <sup>1</sup>Prarthi Bhatt, <sup>2</sup>Prof..Devang shah

<sup>1</sup>Electronics and Communication Engineering, <sup>2</sup> Assistant professor, <sup>1</sup>VLSI & Embedded system Design, , <sup>2</sup>Electronics and communication Engineering, <sup>1</sup>GTU PG SCHOOL, Gandhinagar, Gujarat, India, <sup>2</sup>L.J.Institude of Engineering and Technology.

Abstract—The purpose of this project is to design and verify of AMBA based AHB to AHP bridge. AHB2APB Bridge is a complex interface between Advance high performance bus (AHB) and Advance peripheral bus (APB) .AHB2APB Bridge will be communicate between low bandwidth peripheral on APB with high bandwidth ARM processors and high speed device on (AHB). So, there will be no data loss between AHB to APB or APB to AHB data transfers.

Index Terms—AMBA bus, AHB bus, APB bus, SOC

#### I. INTRODUCTION

The Advance microcontroller bus Architecture (AMBA) are standard for on chip bus architecture. On chip bus architecture plat a very important role in SOC system. The AMBA is used to interconnect the component of module .It will maintain the intercommunication of functional blocks on system on chip<sup>[1]</sup>. The AMBA will provide a efficient way to interconnect the components and increase the performance of the system. AMBA have an advantage that it is open specification.

The Advanced Microcontroller Bus Architecture protocol describes number of buses and interfaces. In its first version which Introduced in 1996 by ARM were advance system bus and in its second version 2 in 1999, it defines AMBA 2.0, which is a high performance bus. Advance high performance bus is a signal clock edge protocol. In 2003, ARM introduced its third generation version AMBA 3.0 which includes AXI<sup>[6]</sup>. The first version of AMBA contains only one peripheral bus with two system bus.

Three bus specifications are there in AMBA as follow-

- 1. Advanced High- Performance Bus (AHB).

- 2. Advanced System Bus (ASB).

- 3. Advanced Peripheral Bus (APB).

# 1.1 Advance high Performance bus (AHB)

In 1999 ARM introduced second version AMBA 2.0, which is a high performance bus and synthesizable design .AHB has high bandwidth, which makes a best choice among a APB and ASB. AHB is high performance and high clock frequency system module<sup>[8]</sup>. This bus provide high bandwidth interface between the Elements of transfer. AHB support multiple masters and provide high bandwidth performance. The AHB bus acts as a high performance systembackbone<sup>[1]</sup>.

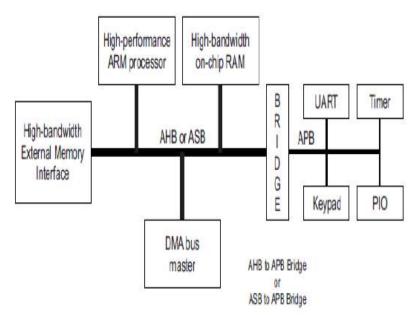

The AHB bus support interconnection between high performance ARM processor, high bandwidth on chip RAM, high bandwidth external memory interface and DMA bus. There is a bridge between high performance bus (AHB) and low bandwidth peripheral bus (APB) for efferent data transfer.

## 1.2. The Advance System Bus (ASB)

The First Version of AMBA introduced Advance System Bus in 1996. The AMBA based ASB is for high frequency system modules. ASB is system bus which is suitable for use where the high-performance features of AHB are not required. ASB also supports the efficient connection of processors, on-chip memories and off-chip external memory interfaces with low-power peripheralfunctions<sup>[6]</sup>.

# 1.3 The Advance Peripheral Bus (APB)

ARM introduced second version in 1999, it defines AMBA 2.0, which is a high performance bus. The APB is low power consumption and low frequency system module<sup>[7]</sup>. The APB reduces complexity for interfacing with peripheral. APB can be used for small area and less power with either version of the system. The APB protocol is the bus protocol employed for the peripherals like UART, Keypad, PIO, Timer, LCD Display or LED display etc.

# 2 AHB to APB Bridge

AHB2APB Bridge is a interface between Advance high performance bus (AHB) and Advance peripheral bus (APB) .Bridge provide communication between low frequency peripheral on APB with high frequency and high speed device on (AHB). Bridge provide efficient data a transfer from AHB to APB<sup>[6]</sup>. So, there is no data loss between AHB to or from APB during data transmission. Here, Handshaking Signaling method will use to transfer data between AHB and APB<sup>[1]</sup>.

Figure 2.1: AMBA Architecture<sup>[3]</sup>

Bridge FSM is used to transmit data from AHB to APB.AHB will send valid address and write data to APB. The address, control and data from AHB will control the peripheral of APB. If valid is high write signal is low of AHB then read transfer is perform. Write transfer is perform from AHB to APB and read transfer is perform from APB to AHB<sup>[2]</sup>. When valid and write both signal is high then write transfer is perform. Read and Write transfer is complete in two cycles and enable signal will assert at second cycle and drive low at thirdcycle<sup>[6]</sup>. Pipeling structure is to transmit data because APB is slow to transmit data, So AHB has to wait for APB to complete the transfer. For burst transfer wait state is used in write transfer<sup>[6]</sup>.

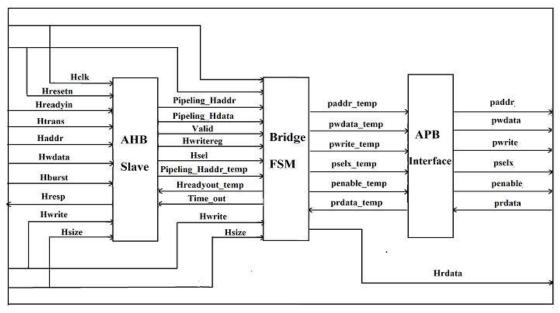

## 3. Architecture of AHB to APB Bridge

The Architecture of AHB to APB is given on the Figure 3.1. As shown in figure 3.1 architecture has three modules. In this Architecture data will transfer from APB master to AHB slave Bridge. FSM is used for interface between low bandwidth APB and high bandwidth AHB. Pipelining structure is use in FSM to transfer data from APB to AHB. A wait state is use transfer data to or from APB, because APB has low bandwidth so its transfer speed is slow, so AHB need to wait until APB complete the read or write transfer [6].

In AMBA based AHB master will initialize the operation by sending address and control signal to AHB Slave. After that AHB Slave will send read and write data to AHB master as per the address and control given by AHB slave. Then AHB master will send Hready signal to AHB slave, which indicate that transfer has done<sup>[2]</sup>.

Figure 3.1:. Architecture of AHB to APB Bridge

To solve the existing problem a time counter is used in APB interface. When AHB master is failed to send Hready signal, after some time timer counter signal will drive high and APB interface can start another transfer or resend the read data to AHB slave, this will increase the performance of the system.

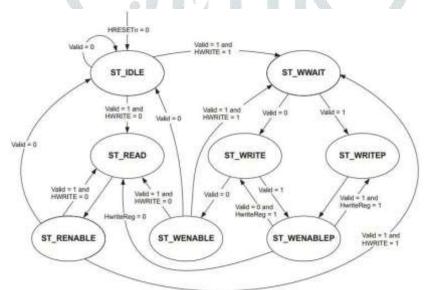

#### 4. State Machine of AHB to APB

AHB to APB Bridge FSM is use for communication between AHB protocol and APB Protocol. The State machine of AHB to APB Bridge FSM is shown in Fig 4.1.AHB to APB bridge State machine has 8 states. Description of all the stage is given below.

FSM is used for interface between low bandwidth APB and high bandwidth AHB. Pipelining structure is use in FSM to transfer data from APB to AHB.A wait state is use transfer data to or from APB, because APB has low bandwidth so its transfer speed is slow, so AHB need to wait until APB complete the read or write transfer<sup>[6]</sup>.

#### ST IDLE:

IN this state APB buses and Pwrite will hold the last value they had and Pselx and PENABLE will be low.

The ST IDLE state is entered from:

- This state is entered when Hresetn is zero.

- When there is no peripheral to perform ST IDLE state is entered from ST RENABLE, ST WENABLE, ST IDLE.

## The next state:

- ST\_READ: for a read transfer, when AHB contains valid APB read transfer

- ST\_WWAIT: for write transfer, when AHB contains valid APB write transfer.

#### ST READ:

In this state address is decoded and Haddr is driven in Paddr and Pselx line is driven high and Pwrite is driven low. In this state data is read from APB to AHB.A wait state is use ensure AHB read data transfer do not complete until APB drives read data on Hrdata  $The \ ST\_READ \ state \ entered \ from \ ST\_IDLE, \ ST\_RENABLE, \ ST\_WENABLE, \ when \ read \ transfer \ has \ to \ perform.$

The next state is always ST\_RENABLE

Figure 4.1: State machine of AHB to APB<sup>[6]</sup>

# ST\_WWAIT:

The wait state is use for Pipeling structure of AHB transfer, to allow to complete AHB write data transfer so that write data is driven on a Hwdata. The APB write transfer is start in next cycle after write data is driven in Hwdata.

The ST\_WWAIT state is entered from ST\_IDLE, ST\_RENABLE, ST\_WENABLE, when write transfer is need to perform.

The next state is always ST WRITE.

#### ST WRITE:

In this state address is decoded and Haddr is driven in Paddr and Pselx line and Pwrite line driven high. Single transfer is done in ST\_WRITE

The ST\_WRITE state is entered from:

- ST\_IDLE: when there are no more peripheral to perform the transfer.

- ST\_WENABLEP: when there are no more peripheral to perform the transfer and current pending transfer is write.

#### The next state:

- ST\_WENABLE: When there are no more peripheral to perform the transfer.

- ST WENABLEP: When there are one more peripheral to perform the transfer.

#### ST WRITEP:

In this state address is decoded and Haddr is driven in Paddr and Pselx line and Pwrite is driven high. More than one transfer is done in ST\_WRITEP state. A wait state is use because AHB bandwidth is high and APB bandwidth is low so there will be always one pending transfer between current AHB peripheral transfer and current APB peripheral transfer.

#### ST RENABLE:

In this state Penable is driven high and it will enable the read transfer of APB

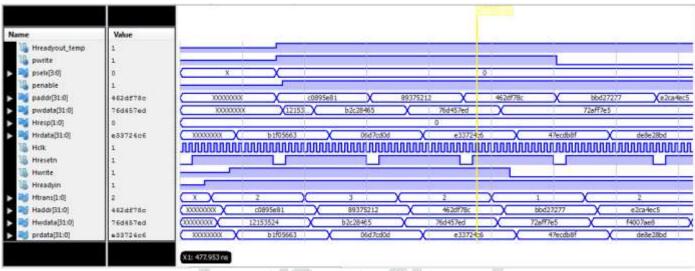

# 5 .Implementation and Result

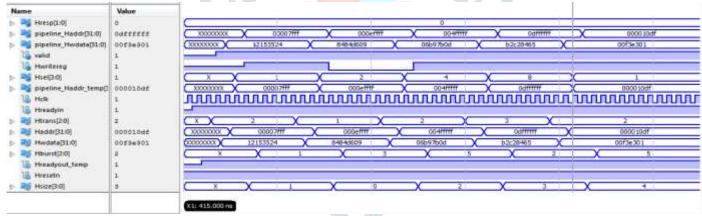

Waveform of top module of AHB to APB bridge is shown in figure 5.1

Figure 5.1 Simulation result of AHB to APB top module

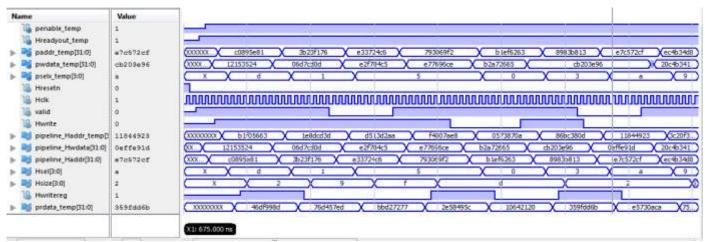

Waveform of AHB slave is shown in figure 5.2

Figure 5.3 Simulation result of AHB\_slave

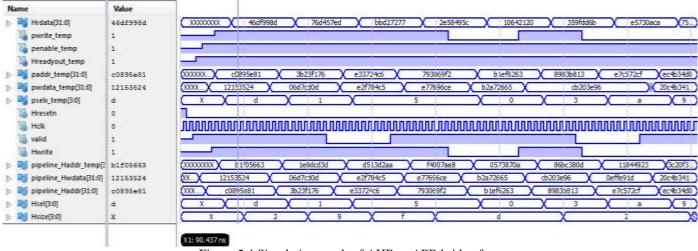

Waveform of AHB to APB bridge fsm is shown in figure 5.3

Figure 5.3 Simulation result of AHB to APB bridge fsm

Waveform APB interface is shown in figure 5.4

Figure 5.4 Simulation result of AHB to APB bridge fsm

## 6. Acknowledgement

I am gratefully thanks to my project mentor Mr. Vishnu Vaishnav in order to guide me throughout the way. It was his keen interest, encouragement and full cooperation that have made it possible for me to move ahead with the work. I would also like to thank my External guide Prof. Devang Shah whose guidance had inspired me for this work. I collected various information about this project paper from browsing the Internet, Real life experience, Different types of journals and many other sources. After that gaining proper knowledge I have prepared this literature review report. Finally, I am very much grateful to my Parents and Sister who always gave me constant support and encouragement. I hope that this paper has been prepared for the fulfillment of the course requirement

## 7. Conclusion.

The implemented communication bridge between AHB and APB was designed and implemented in Xilinx ISE 14.1, spectrum 6, using Verilog HDL .The design topmodule of AHB2APB bridge is completed successfully. The design AHB slave, AHB2APB bridge FSM and APB interface is completed successfully.

# 8. References

- [1] Vani.R.M † and M.Roopa ††, "Design of AMBA Based AHB2APB Bridge Vani.R.", IJCSNS International Journal of Computer Science and Network Security, VOL.10 No.11, November 2010

- [2] Prof. Ravi Mohan Sairam, Prof. Sumit Sharma, Miss. Geeta Pal," FSM & Handshaking Based AHB to APB Bridge for High Speed Systems", International Journal of Engineering Research & Technology (IJERT)Vol. 2 Issue 11, November – 2013

- [3] Mrs Sowmya Aithal 1, Dr. J.S. Baligar 2, Guruprasad S.P. 3, Mrs Sowmya Aithal, IJECS Volume 05 Issue 5 May 2016 Page No.16617-16619 Page 16617,"FPGA Implementation of AHB to APB Protocol", International Journal Of Engineering And Computer Science ISSN: 2319-7242 Volume 5 Issue 5 May 2016

- [4] Sangik Choi and Shinwook Kang, "Implementation of an On-Chip Bus Bridge between Heterogeneous Buses with Different Clock Frequencies", IEEE 2005

- [5] Massimo Conti, Marco Caldari, Giovanni B. Vece, Simone Orcioni, Claudio Turchetti, "Performance Analysis of Different Arbitration Algorithms of the AMBA AHB Bus", IEEE 2004

- [6] AMBA University Kit Technical Reference Manual

- [7] AMBA<sup>TM</sup> 3 APB Protocol v1.0 Specification

- [8] AMBA® 3 AHB-Lite Protocol v1.0 specification